程序访问的局部性原理

程序访问的局部性原理包括时间局部性和空间局部性。

- 空间局部性:在最近的未来要用到的信息(指令和数据),很可能与现在正在使用的信息在存储空间上是邻近的

- 时间局部性:在最近的未来要用到的信息,很可能是现在正在使用的信息

高速缓冲技术是利用程序访问的局部性原理,把程序中正在使用的部分存放在一个高速的、容量较小的Cache中,使CPU的访存操作大多数针对Cache进行,从而大大提高程序的执行速度。

Cache的基本工作原理

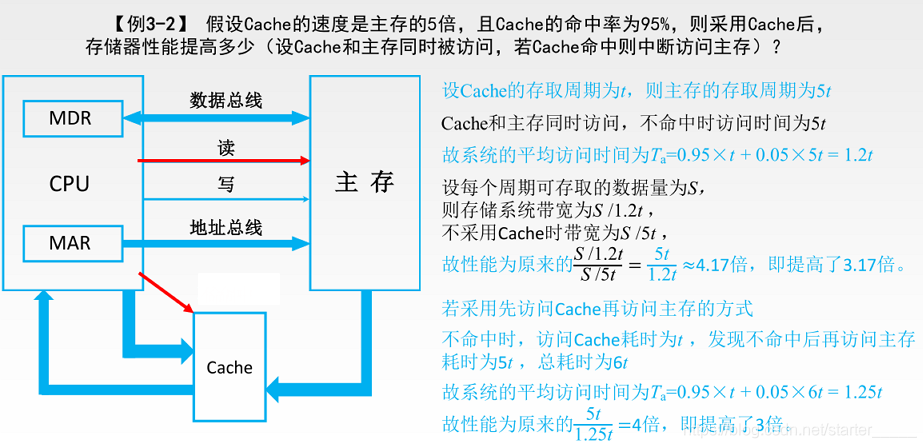

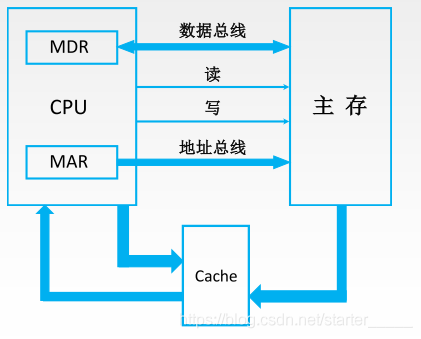

Cache位于存储器层次结构的顶层,通常由SRAM构成。

Cache和主存都被分成若干大小相等的块(Cache块又称为Cache行),每块由若干字节组成,块的长度称为块长(Cache行长)。所以Cache中的块数要远少于主存中的块数,它仅保存主存中最活跃的若干块的副本。

CPU与Cache之间的数据交换以字为单位,而Cache与主存之间的数据交换则以Cahce块为单位。

当CPU发出读请求时,若访存地址在Cache中命中,就将此地址转换成Cache地址,直接对Cahce进行读操作,与主存无关;若访存地址在Cache中未命中,则需访问主存,并把此字所在的块一次性地从主存调入Cache,若此时Cache已满,则需根据某种 替换算法,用这个块替换Cache中原来的某块信息。

当CPU发出写请求时,若Cache命中,有可能会遇到Cache与主存中的内容不一致的问题,此时需要根据某种 写策略 解决这个问题。

Cahce的性能指标

与Cahce有关的性能指标主要有:命中率,缺失率和平均访问时间。

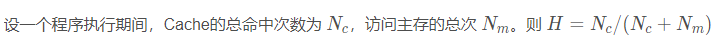

1. 命中率H

- CPU欲访问的信息已在Cache中的比率

2. 缺失率M

- CPU欲访问的信息不在Cache中的比率

M=1−H

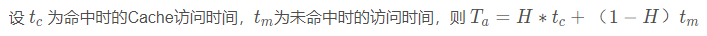

3. 平均访问时间 Ta